During the switching process of the MOS, the gate voltage is prone to oscillation, generating very high or very low voltage spikes. The externally measured Vgs value may far exceed the maximum value allowed in the device specification sheet. Users often worry that excessive gate stress may lead to damage to the device's gate.

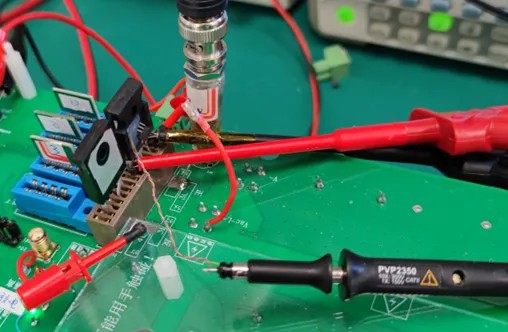

The measured MOS turn off waveform is as follows:

The measured MOS open waveform is as follows:

Summary

In addition, measuring the external Vgs voltage during the operation of high-voltage devices is also difficult, as common measurements often use differential probes. It is necessary to pay attention to the common mode suppression performance of differential probes at high frequencies (often 100MHz), as poor common mode suppression performance cannot accurately measure the external Vgs voltage. So using an optically isolated probe is an ideal method for measuring external Vgs voltage.